# University of California, Santa Barbara

Department of Electrical and Computer Engineering

ECE 152A – Digital Design Principles

Homework #4 – Solution

#### Problem #1.

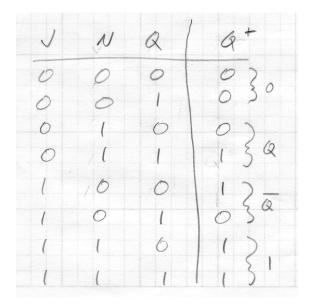

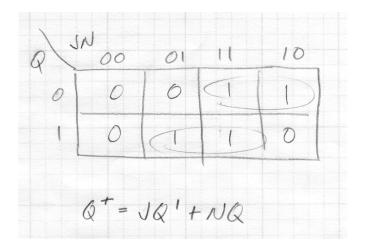

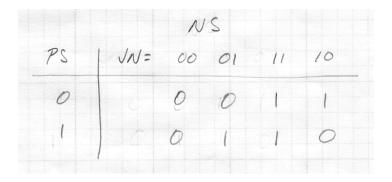

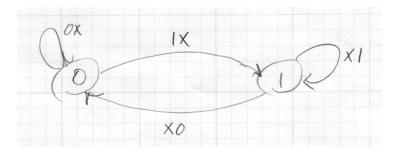

A JN flip flop is constructed by (internally) complementing the K input to an otherwise normal JK flip flop. For the JN flip flop, derive the following:

1. The characteristic table

2. The characteristic equation

Homework #4 Solution – Page 1 of 31

3. The state table

4. The state diagram

5. The excitation table

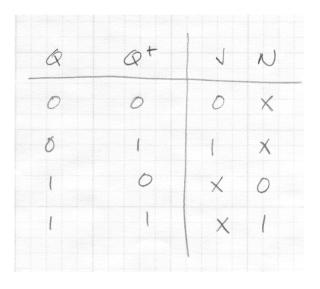

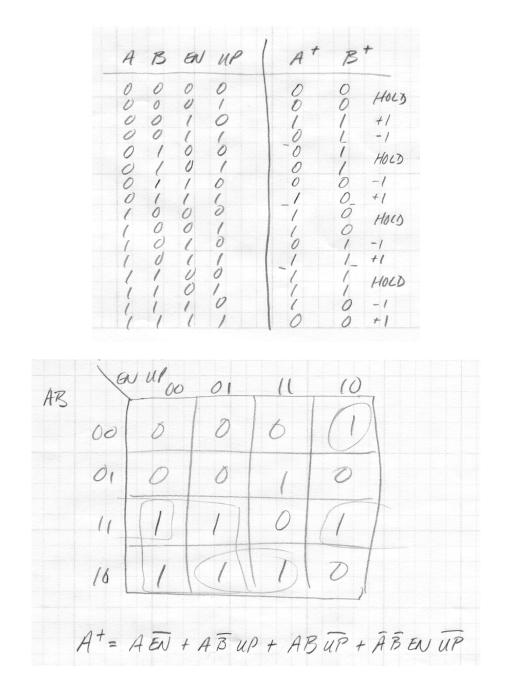

# Problem #2.

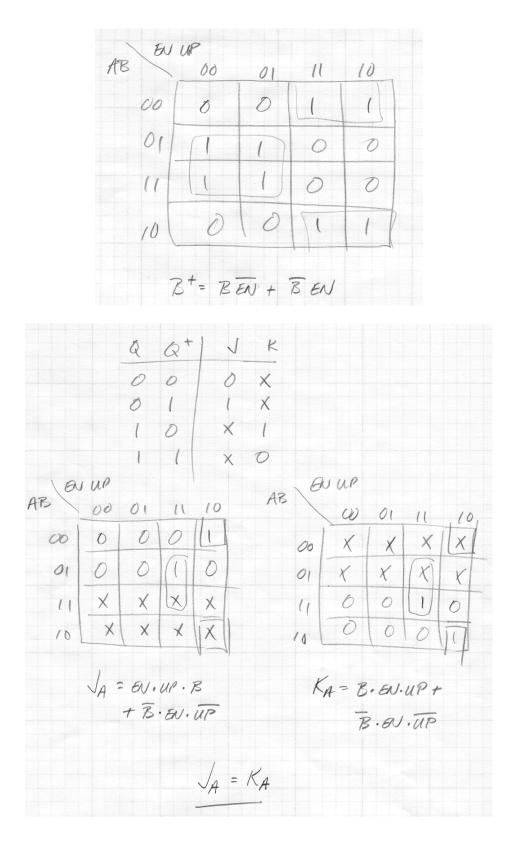

Design a 2-bit, binary up/down counter. The counter has 2 inputs, up\_down and enable. The truth table below defines the operation of the counter:

| enable | up down | operation       |

|--------|---------|-----------------|

| 0      | 0       | hold count      |

| 0      | 1       | hold count      |

| 1      | 0       | decrement count |

| 1      | 1       | increment count |

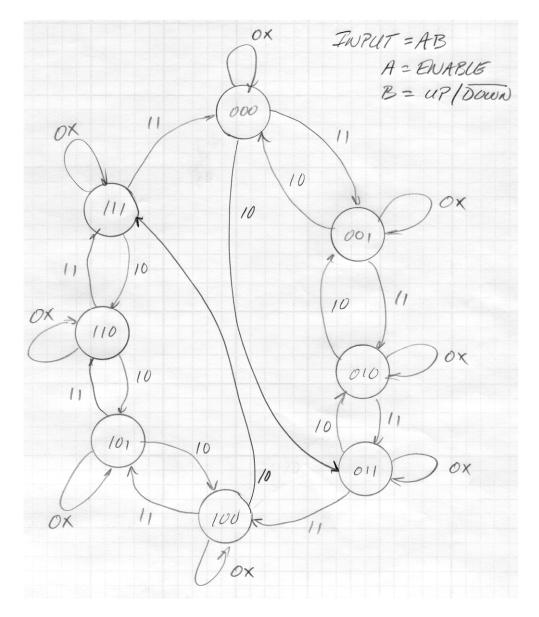

Use positive edge triggered JK flip flops. In your answer, include (1) a state diagram, (2) a state table, (3) a next state map and (4) all Kmaps used in determining flip flop inputs

# Problem #3.

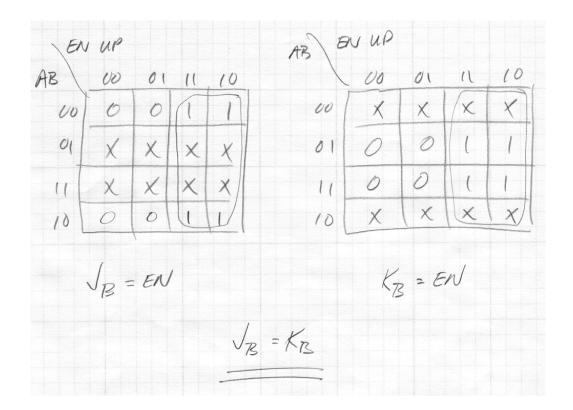

Design a three bit counter with a single input called **mode**. The counter counts in binary if the mode bit is zero, and counts in gray code if the mode bit is one (recall the three bit gray code is 000, 001, 011, 010, 110, 111, 101, 100). The mode bit can change at any time during the count sequence and your counter should begin counting in the new mode on the next clock input.

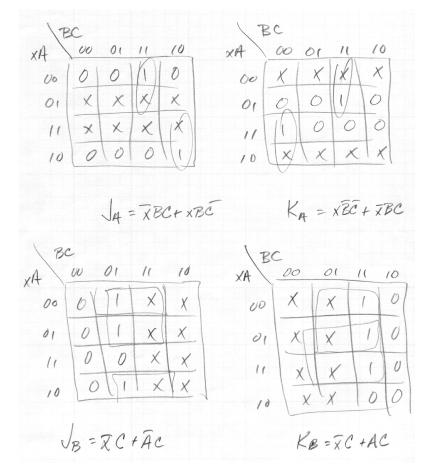

Design the counter using JK flip flops. You don't have to draw the logic diagram, specifying the J and K inputs to each flip flop is sufficient. Use A, B and C as the state variable names.

Include (1) a state table, (2) next state maps and (3) K-maps for all flip flop inputs.

8/3/2009

|   |   | - | N | IUDE | =0 | MODE=1 |

|---|---|---|---|------|----|--------|

| A | B | C | A | B    | C  | ABC    |

|   | 0 |   | 0 | 0    | 1  | 001    |

| 0 | 0 | 1 | 0 | 1    | 0  | 011    |

| 0 | 1 | 0 | 0 | 1    | 1  | 110    |

| 0 | 1 | 1 | 1 | 0    | 0  | 010    |

| 1 | 0 | 0 | 1 | 0    | 1  | 000    |

| 1 | 0 | 1 | 1 | 1    | D  | 100    |

| 1 | 1 | 0 | 1 | 1    | 1  | 1 1 1  |

| 1 | ( | 1 | 0 | 0    | 0  | 101    |

Homework #4 Solution - Page 7 of 31

Homework #4 Solution - Page 8 of 31

# Problem #4.

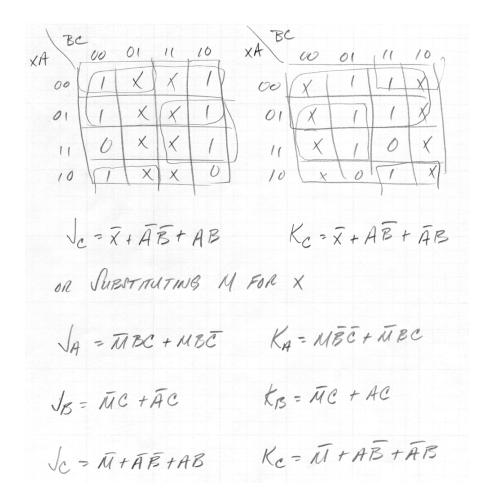

Consider the flip flop illustrated below:

1. Would this flip flop function as a positive (rising) or negative (falling) edge

Homework #4 Solution – Page 9 of 31

triggered flip flop (and why)?

NEGATIVE (OR FALLING) EDGE TRIGGERED BECAUSE SLAVE IS ACTIVE ON LOW PHASE OF CLOCK

2. Construct the characteristic table for this flip flop.

CHARACTERISTIC TABLE NOTE: MASTER IS ACTIVE ON HIGH PHASE OF CLOCK; A=B=O NOT ALLOWED BECAUSE THIS WOULD RESULT IN XM = YM = 1 Q t A B Q 0 0 0 NOT ALLOWED 0 0 0 0 1 1 1 0 0 0 1 0 1 0 HOLD

3. What modifications are necessary to transform this into a D flip flop (the output Q should take the value of the single input D after the active clock edge)?

NOTE FROM CHARACTERISTIC TABLE THAT Q FOLLOWS A WHEN A \$ B APPLY D DIRECTLY TO A INPUT; APPLY TNUERTED D TO B INPUT

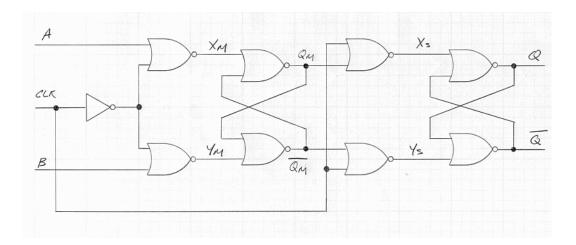

4. What modifications are necessary to transform this into a JK flip flop (the outputs Q and Q' should toggle after the active clock edge when A and B = 0)?

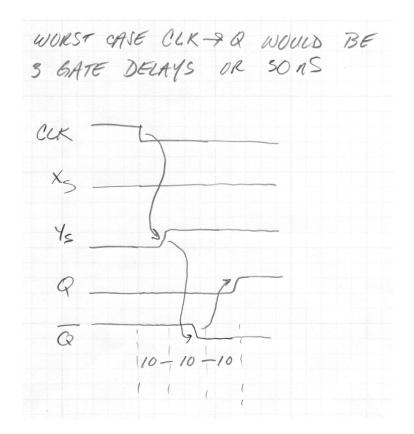

5. If all the gates have a propagation delay of 10 ns (both  $t_{PLH}$  and  $t_{PHL}$ ), what would the worst case CLK to Q delay be?

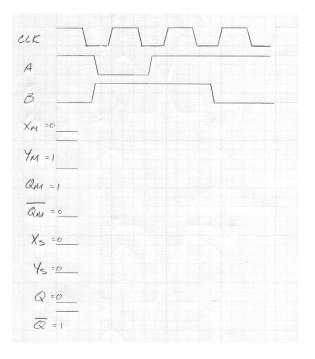

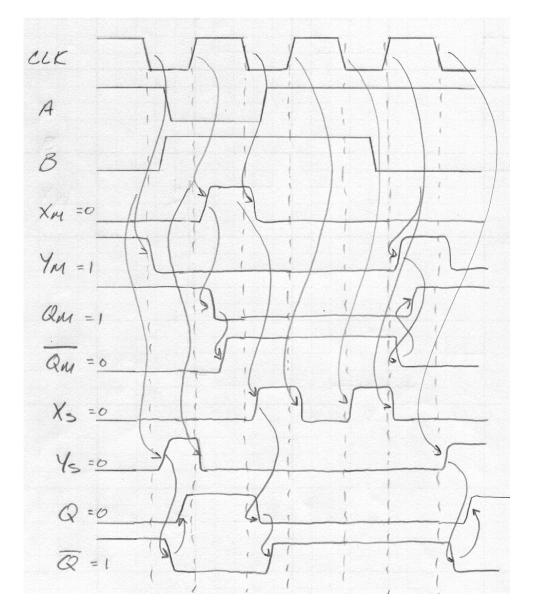

6. Complete the timing diagram on the following page. Include arrows indicating the relationship and order of signal transitions. Assume the clock period is much greater than the gate delays. The initial conditions are noted on the timing diagram.

Homework #4 Solution - Page 12 of 31

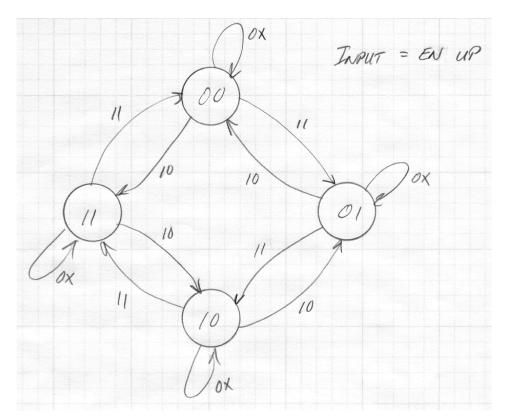

#### Problem #5.

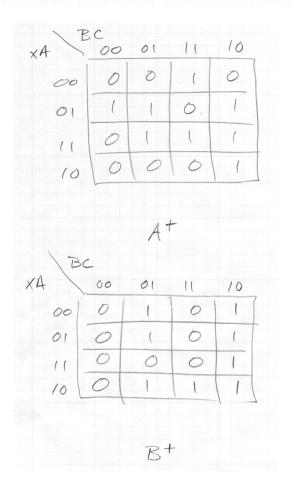

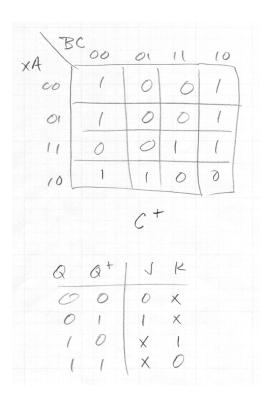

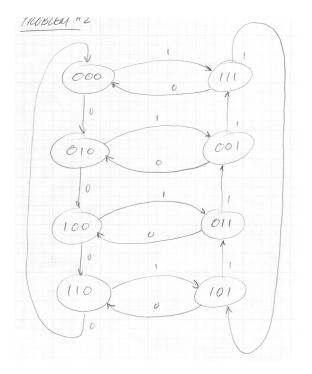

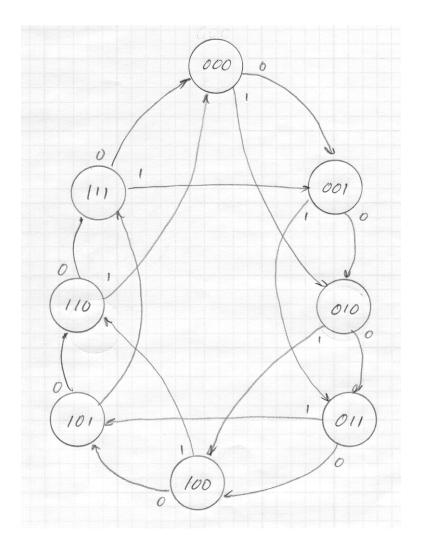

In this problem you are to design a 3-bit counter having a single control input: x. When x is 0, the counter counts up in even numbers (0,2,4,6,0,...). When x is 1, the counter counts down in odd numbers (7,5,3,1,7,...).

When the input changes, the count sequence should change appropriately from the current count. For example, if the current count is 4 and x changes from 0 to 1, the next count should be 3. If the current count is 5 and x changes from 1 to 0, the next count should be 6, etc.

Implement your design using T flip flops. Note that the state diagram is the most important part of the design. Any error in the state diagram will ripple throughout the design.

# Include the following:

1. A state diagram

# 2. A state table

3. Next state maps for the three flip flops

- 4. Karnaugh maps for the three T inputs

- 5. Simplified equations for the three T inputs

# Problem #6.

This problem deals with the minimum clock period (or maximum frequency) of a digital system which generates a parity bit for a 3 bit data word. A parity bit is added to a data word to allow for single bit error detection and either even or odd parity can be implemented. In even parity, the total number of bits (including the parity bit) is an even number.

The truth table below illustrates the generation of an even parity bit for a 3-bit data word.

| A | В | С | Even Parity Bit |

|---|---|---|-----------------|

|   |   |   |                 |

| 0 | 0 | 0 | 0               |

| 0 | 0 | 1 | 1               |

| 0 | 1 | 0 | 1               |

| 0 | 1 | 1 | 0               |

| 1 | 0 | 0 | 1               |

| 1 | 0 | 1 | 0               |

| 1 | 1 | 0 | 0               |

| 1 | 1 | 1 | 1               |

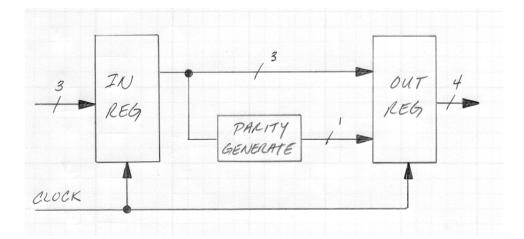

The block diagram for the complete digital system is given below:

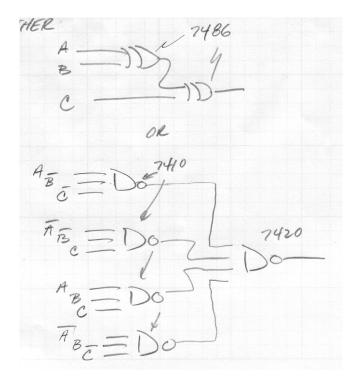

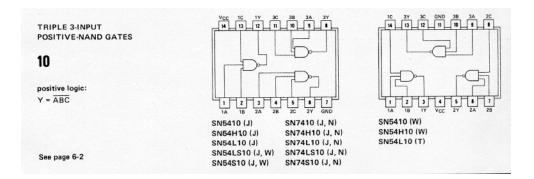

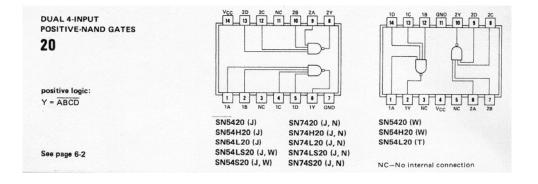

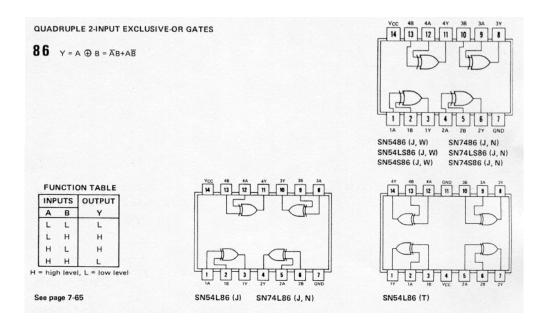

The parity generate block is the implementation of the combinational circuit defined in the truth table on the previous page. Based on that truth table, design the circuit using any combination of 7410's (3 input NAND gates), 7420's (4 input NAND gates) or 7486 (2 input XOR gates). Pinouts and switching characteristics for these devices are included on the following pages.

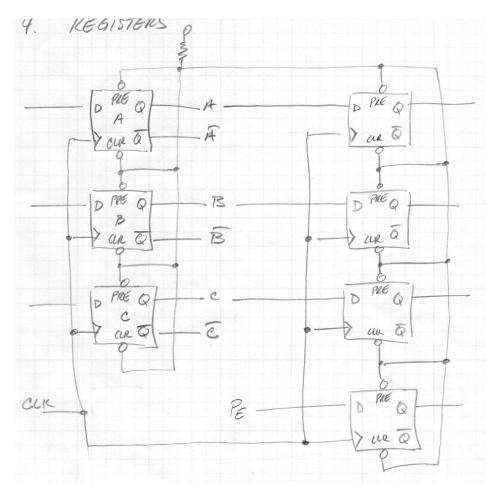

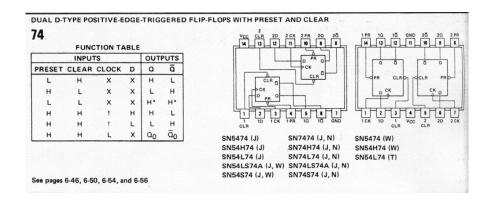

The input and output registers are to be implemented using 7474 D flip flops. The pinout and switching characteristics for this device are also included on the following pages. The specific characteristics for the 7474 are circled (other devices are also described on this table).

Include the following in your answer:

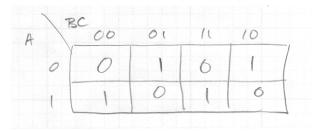

1. A Karnaugh map for the parity generate circuitry.

2. The minimized Boolean equation for the parity generate circuitry.

PE = ABC + ABC + ABC + ABC = ABBBC

3. A logic diagram indicating which gates are used for the parity generate circuitry and how they are interconnected.

4. A logic diagram indicating how the 7474's are used to implement the input and output registers. Indicate what is done with all inputs and outputs (clock, preset, clear, Q, Q' and D).

5. A calculation of the minimum clock period necessary for your implementation to function properly. Include the equation you used to determine the minimum clock period and which numbers from the data sheet were selected and incorporated into this calculation.

#### 7410, 7420 Switching Characteristics

| түре     | TEST<br>CONDITIONS#                   |      | tPLH (ns)<br>Igation delay<br>p-high-level o |     |     | tpHL (ns)<br>Igation delay<br>to-low-level o |     |

|----------|---------------------------------------|------|----------------------------------------------|-----|-----|----------------------------------------------|-----|

|          |                                       | MIN  | TYP                                          | MAX | MIN | TYP                                          | MAX |

| '00, '10 |                                       | 1000 | 11                                           | 22  |     | 7                                            | 15  |

| '04, '20 | $C_{I} = 15  pF, R_{I} = 400  \Omega$ |      | 12                                           | 22  |     | 8                                            | 15  |

| '30      | 1                                     |      | 13                                           | 22  |     | 8                                            | 15  |

|          |                                       |      |                                              |     |     |                                              |     |

#### 7486 Switching Characteristics

| PARAMETER¶       | FROM<br>(INPUT) | TEST CON         | DITIONS              | MIN | түр | MAX | UNIT |

|------------------|-----------------|------------------|----------------------|-----|-----|-----|------|

| tPLH             |                 |                  |                      |     | 15  | 23  |      |

| tPHL .           | A or B          | Other input low  | CL = 15 pF,          |     | 11  | 17  | ns   |

| <sup>t</sup> PLH | A or B          |                  | $R_L = 400 \Omega$ , |     | 18  | 30  |      |

| <sup>t</sup> PHL | AOFB            | Other input high | See Note 3           |     | 13  | 22  | ns   |

# 7474 Switching Characteristics

|                                   |                     | SERIES 54/74 |      | '70 |      |      | 72, '73, 76, '107 |     |      | '74 |      |      | 109 |      |      | '110 |      |      | '111 |      | UNIT |

|-----------------------------------|---------------------|--------------|------|-----|------|------|-------------------|-----|------|-----|------|------|-----|------|------|------|------|------|------|------|------|

|                                   |                     |              | MIN  | NOM | MAX  | MIN  | NOM N             | AX  | MIN  | NOM | MAX  | MIN  | NOM | MAX  | MIN  | NOM  | MAX  | MIN  | NOM  | MAX  |      |

|                                   |                     | Series 54    | 4.5  | 5   | 5.5  | 4.5  | 5                 | 5 5 | 4.5  | 5   | 5.5  | 4.5  | 5   | 5.5  | 4.5  | 5    | 5.5  | 4.5  | 5    | 5.5  | V    |

| Supply voltage, VCC               |                     | Series 74    | 4.75 | 5   | 5.25 | 4.75 | 5 5               | .25 | 4.75 | 5   | 5.25 | 4.75 | 5   | 5.25 | 4.75 | 5    | 5.25 | 4.75 | 5    | 5.25 |      |

| High-level output curren          | nt, IOH             |              |      |     | -400 |      | -                 | 400 |      |     | -400 |      |     | -800 |      |      | -800 |      |      | -800 | μA   |

| Low-level output curren           | t, IOL              |              |      |     | 16   |      |                   | 16  |      |     | 16   |      |     | 16   |      |      | 16   |      |      | 16   | mA   |

|                                   | Clock high          |              | 20   |     |      | 20   |                   |     | 30   |     |      | 20   |     |      | 25   |      |      | 25   |      |      |      |

| Pulse width, tw                   | Clock low           |              | 30   |     |      | 47   |                   |     | 37   |     |      | 20   |     |      | 25   |      |      | 25   |      |      | ns   |

|                                   | Preset or clear low | 1            | 25   |     |      | 25   |                   |     | 30   |     |      | 20   |     |      | 25   | -    |      | 25   |      |      |      |

| Input setup time, t <sub>su</sub> |                     |              | 20   | t   |      | 01   | 1                 |     | 201  |     |      | 10   |     |      | 201  |      |      | 01   |      |      | ns   |

| Input hold time, th               |                     |              | 5    | †   |      | 0    | 1                 |     | 5    | 1   |      | 61   |     |      | 51   |      |      | 301  |      |      | ns   |

|                                   |                     | Series 54    | -55  |     | 125  | -55  |                   | 125 | -55  |     | 125  | -55  |     | 125  | -55  | -    | 125  | -55  |      | 125  | °c   |

| Operating free-air tempe          | erature, TA         | Series 74    | 0    |     | 70   | 0    |                   | 0   | 0    | -   | 70   |      |     | 70   | 0    |      | 70   | 0    |      | 70   |      |

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER   | FROM            | то       | TEST                    |     | '70 |     |     | 72, '73 |     |     | '74  |     |     | '109 |     |     | '110 |     |     | '111 |     | UNIT |

|-------------|-----------------|----------|-------------------------|-----|-----|-----|-----|---------|-----|-----|------|-----|-----|------|-----|-----|------|-----|-----|------|-----|------|

| PARAMETER   | (INPUT)         | (OUTPUT) | CONDITIONS              | MIN | TYP | MAX | MIN | TYP N   | AAX | MIN | TYP  | MAX |      |

|             |                 |          |                         | 20  | 35  |     | 15  | 20      |     | 15  | 25   |     | 2   | 33   |     | 20  | 25   |     | 20  | 25   |     | MHz  |

| fmax        |                 |          |                         |     |     | 50  |     | 16      | 25  |     |      | 25  |     | 10   | 15  |     | 12   | 20  |     | 12   | 18  | 0.5  |

| TPLH        | Preset          | u        |                         | -   |     | 50  | -   | 25      | 40  |     |      | 40  |     | 23   | 35  |     | 18   | 25  |     | 21   | 30  |      |

| <b>tPHL</b> | (as applicable) | ā        | CL = 15 pF,             | -   |     |     | -   | 16      | 25  | -   |      | 25  |     | 10   | 15  | -   | 12   | 20  |     | 12   | 18  |      |

| TPLH        | Clear           | a        | R <sub>L</sub> = 400 Ω, | -   |     | 50  |     |         | -   | -   |      | 40  | -   | 17   | 25  |     | 18   | 25  |     | 21   | 30  | ns   |

| TPHL        | (as applicable) | Q        | See Note 2              |     | -   | 50  |     | 25      | 40  | -   | _    |     |     |      | _   | -   | 20   | 30  | -   | 12   | 17  |      |

| TPLH        |                 |          |                         |     | 27  | 50  |     | 16      | 25  |     | . 14 | 25  |     | 10   | 16  |     | _    |     | -   |      |     | 05   |

| tpui        | Clock           | Q or Q   | propagation dela        |     | 18  |     |     | 25      | 40  |     | 20   |     |     | 18   | 28  | -   | 13   | 20  |     | 20   | 30  | 1    |

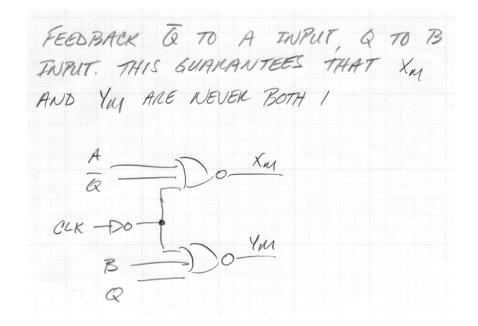

= (CLK->Q) + (COMBO + (SETUP TIME) GATE DELAY) FROM 7474 DATA SHEET MAX CLOCK - Q = 40 15 (tAML) SETUP TIME = 20nS COMBINATIONAL DELAY FOR 7410, 7420 JUPLENENTATION - BECAUSE TRUE AND COMPLEMENTED VERSIONS AVAILABLE FROM FF'S, NO TRUERTERS NECESSARY - Two CASES OUTPUT HIGH: tpm (7410) + tpl (7420) 15 + 22 = 37 OUTPUT LOW: tput (7410) + tpHL (7420) 22 + 15 = 37

FOR 7486 (XOR) IMPLEMENTATION - BECAUSE WORST CASE CONDITION tplat (OTHER FUPAT HIGH) = 30nS CAN OCCUR FOR BOTTH GATES, THIS COMBINATIONAL DELAY NUST BE USED = 60nS MINIMUM CLOCK PERIOD 20 + 37 + 40 = 97nS FOR NANDS 20 + 60 + 40 = 120 ms FOR XOR

#### Problem #7.

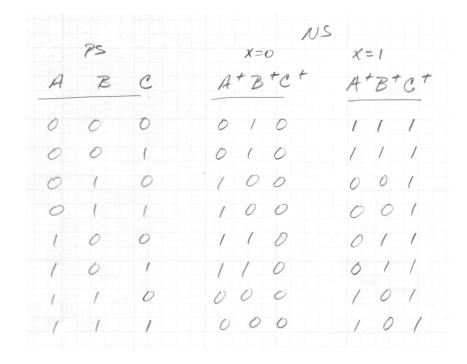

In this problem you are to design a 3-bit counter with a single input (x). When x is 0, the count should be incremented by 1 and when x is 1, the count should be incremented by 2. Label the state variables A, B and C where A is the most significant bit.

1. Generate the state diagram for this counter.

2. Generate the state table for this counter.

|     | NS   |       |  |  |  |  |  |

|-----|------|-------|--|--|--|--|--|

| PS  | X =0 | X = 1 |  |  |  |  |  |

| 000 | 001  | 010   |  |  |  |  |  |

| 001 | 010  | 011   |  |  |  |  |  |

| 010 | 011  | 100   |  |  |  |  |  |

| 011 | 100  | 101   |  |  |  |  |  |

| 100 | 101  | 110   |  |  |  |  |  |

| 101 | 110  | (1)   |  |  |  |  |  |

| 110 | 111  | 000   |  |  |  |  |  |

| 111 | 000  | 001   |  |  |  |  |  |

- BC XA ( ( A+ BC XA Bt

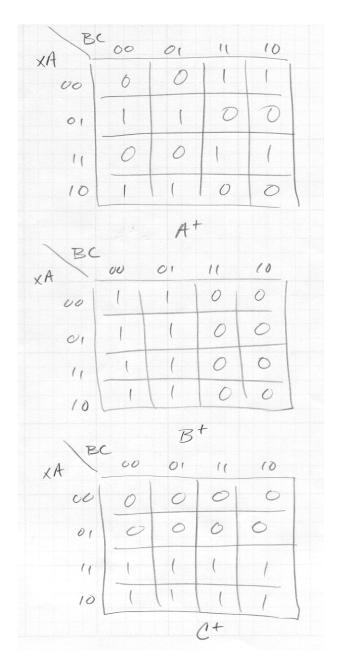

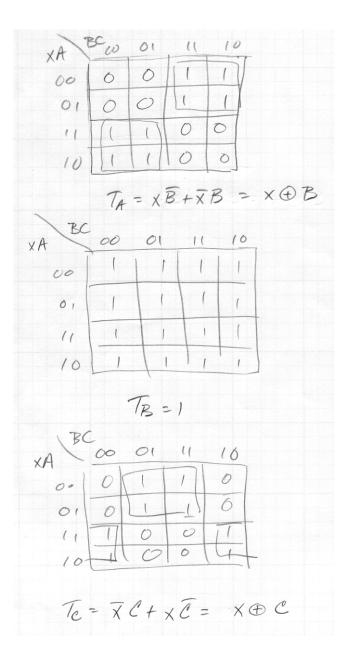

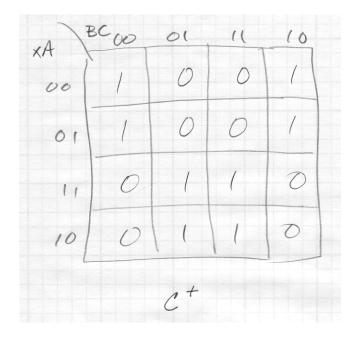

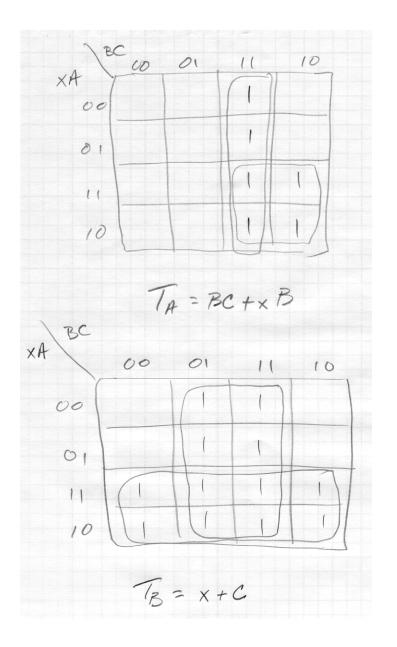

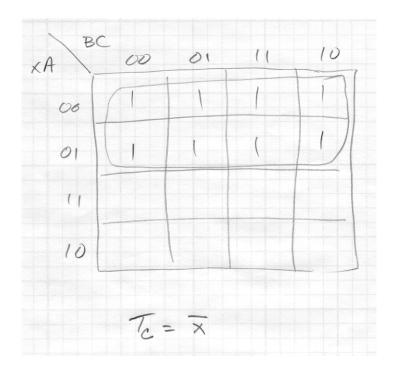

- 3. Generate the next state K-maps for this counter.

4. Implement the design using T flip-flops. Indicate the inputs to the three T flip-flops (the Boolean expression). You don't have to draw the circuit.

#### Problem #8.

This problem addresses Verilog.

1. There are two errors in the code below; identify them and indicate a fix that will allow the code to compile (make any changes necessary but be clear on the changes).

endmodule

1. ASSIGNMENT SYNTAX ERRORS () ASSIGN f = -f DECLARED REG. BUT ASSIGNED TO CONTINUOUSLY (WIRE) FIX: ASSIGN TO PROCEDURALLY (ALWAYS) OR MAKE & A WIRE (2) g= 9 IS REG VARIABLE, SO MUST BE ASSIGNED TO PROCEDURALLY FIX: ADD ALWAYS BLOCK OR MAKE WIRE AND ASSIGN TO CONTINUOUSLY

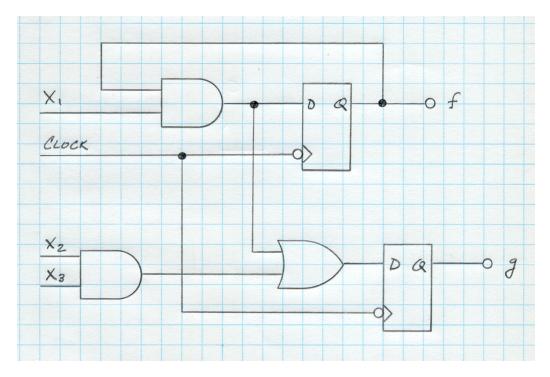

2. For the module below, indicate the circuit that will be synthesized.

endmodule

#### 3. Construct a state diagram for the Verilog code given below

```

module problem4_3 (Clock, A, B, Q);

parameter n=3;

input Clock, A, B;

output [n-1:0] Q;

reg [n-1:0] Q;

always @(posedge Clock)

begin

if (A)

if (B)

Q <= Q + 1;</pre>

```

endmodule